2020 年 9 月 16 日,苹果在秋季第一场新品发布会上推出了 A14 仿生芯片,在 5nm 工艺节点上成功抢得先机。

接下来,犹抱琵琶半遮面的华为麒麟 9000 系列芯片也将在 10 月 22 日随 Mate40 系列手机一起推出,采用的自然也是 5nm 工艺。

而 12 月 1 日 - 2 日,高通会在 2020 年骁龙技术峰会上发布新一代 5nm 旗舰芯片骁龙 875,为安卓终端提供更广泛的支持。

这些芯片排队发布,意味着半导体工艺 5nm 的时代正在全面到来。

其实,当看到 5nm 的苹果 A14 芯片发布时,小编心里突然涌上一阵感慨,半导体的制程工艺,从 10nm 到 7nm 再到现在的 5nm,进化的幅度越来越小,但每进一步,都是整个行业付出巨大研发成本的结果。

相信大家平时刷新利体育(中国)有限公司-官网时已经有所了解,芯片的制程工艺越来越小,等于晶体管越做越小,当工艺越来越接近极限时,难度就会呈指数级上升。

仿佛一个学生,将考分从 60 分提升到 80 分也许不难,但将分数从 95 分提升到 100 分,就很不容易。

最好的例子就是芯片巨头英特尔在 14nm 节点长达 5 年的停滞,一度让 “摩尔定律已死”的言论甚嚣尘上。

好在另一方面,台积电和三星在制程技术上突飞猛进,从 10nm 到 7nm 再到今年的 5nm,一路顺利推进,并超越了英特尔。

尽管后两者在制程名称上有玩 “数字游戏”的成分,但他们对推进半导体制程技术进化、延续摩尔定律所做的贡献有目共睹。

这些年来,芯片制程工艺能够不断微缩,性能可以不断增强,都有赖于整个半导体行业以及学术领域的勇敢创新和不懈努力。

而当节点进一步微缩,5nm 之后的 3nm、2nm、1nm,新的问题又会出现,甚至原来拯救摩尔定律的 3D FinFET 晶体管都将无法应对极限微观世界的要求。

接下来,我们会越来越频繁地听到一个新名词——GAA(环绕式栅极技术晶体管)。

什么是 GAA 环绕式栅极技术晶体管?这篇文章IT之家就和大家一起了解一下。

1、从 3D FinFET 到 GAA,5nm 之后就靠它了

作为取代 3D FinFET 晶体管的全新技术,其实 GAA 环绕式栅极技术晶体管和 3D FinFET 有着千丝万缕的联系,因此我们需要从 3D FinFET 晶体管说起。

在《台积电 5 纳米吊打英特尔 10 纳米?别纠结了,这只是 “数字游戏”》一文中,其实IT之家已经为大家介绍过 3D FinFET 晶体管,这里再简单回顾一下。

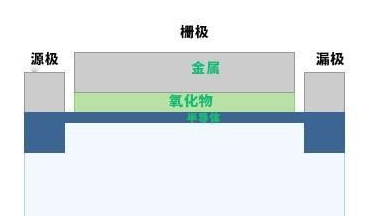

其实所谓晶体管,用通俗易懂的话来讲,就是用半导体材料制作的电流开关结构。左边一个源极(半导体),右边一个漏极(半导体),中间加个栅极(金属),让栅极来控制电流从源极到漏极的通断。

在过去,栅极和源极、漏极之间接触的地方是一个平面,形状差不多是一个矩形,栅极正是依靠这个接触面来对源极和漏极的电流进行控制。

可是,晶体管越做越小,这个接触面的宽度(其实就是栅极的宽度)也越来越窄,当窄到一定程度时(大概是 20nm 左右),栅极对电流的控制力就会大幅减弱。

控制力减弱,就会导致源极的电流穿透栅极,直接和漏极导通,这种情况叫漏电。很显然,漏电不是个好事情,它会导致芯片发热量急剧上升。

所以半导体工艺进化之路在 20nm 左右曾一度面临停滞,摩尔定律遭受威胁。

怎么办呢?其实只要栅极和源极、漏极之间的接触面积足够大,就能控制住电流。这个接触面的宽度不能增加,那就只能增加长度了。

1999 年华人教授胡正明带领加州大学伯克利分校的研究团队发明了 FinFET 晶体管技术和 UTB-SOI 技术,解决了上面说的问题。

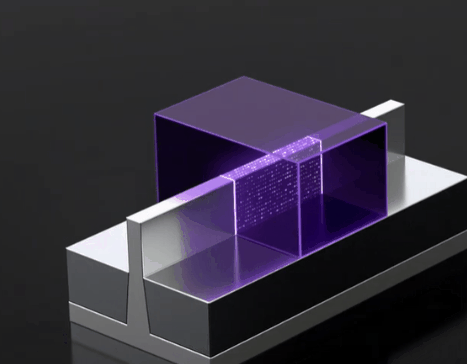

其中,FinFET 晶体管技术是我们听过最多的。它的解决思路就是改造晶体管的结构,将源极和漏极做成像鳍片一样直立的样子,然后让栅极三面包围住鳍片,就像下面这样。

这样,等于是让栅极的宽度不变,通过巧妙地增加长度,来大大增加接触面积,从提升对电流的控制。

换句话说,原来只有一个接触面,现在有三个了,哪怕栅极宽度在进一步缩小,也不怕。

由于这种鳍片结构是立体的形态,所以也叫做 3D FinFET。

3D FinFET 技术的出现解决了晶体管工艺缩小引发的漏电的问题,让半导体的制程可以进一步推进。

随后,经过十多年的产业化推进,英特尔在 2011 年首先推出了使用 22nm FinFET 工艺的第三代 Core 处理器,这标志着摩尔定律的延续。

胡正明教授也被人们称为 FinFET 教父,以及 “拯救摩尔定律的男人”。

而 3D FinFET 技术也伴随着半导体产业发展,一路走到今天的 7nm、5nm 时代。

但是,随着芯片制程的进一步微缩,到了 5nm 之后的 3nm、2nm 等等,3D FinFET 也将迎来它的极限,鳍片距离太近、漏电重新出现,物理材料的极限都让 3D FinFET 晶体管难以为继。

还有随着工艺微缩,假如原来一个 FinFET 晶体管上可以放三个鳍片,现在只能放一个,所以就得把鳍片增高。可是鳍片越来越高,到一定高度后,很难在内部应力作用下保持直立,FinFET 结构就很难形成了。

总之就是,5nm 之后,3D FinFET 也不能用了。

这时候,就轮到 GAA 环绕式栅极技术晶体管技术登场了。

GAA 全称 Gate-All-Around ,是一种环绕式栅极技术晶体管,也叫做 GAAFET。它的概念的提出也很早,比利时 IMEC Cor Claeys 博士及其研究团队于 1990 年发表文章中提出。

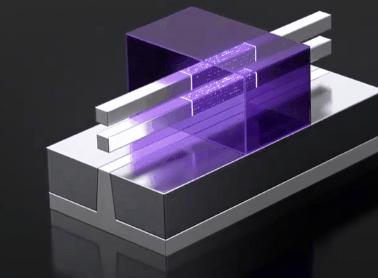

其实 GAAFET 相当于 3D FinFET 的改良版,这项技术下的晶体管结构又变了,栅极和漏极不再是鳍片的样子,而是变成了一根根 “小棍子”,垂直穿过栅极,这样,栅极就能实现对源极、漏极的四面包裹。

看起来,好像原来源极漏极半导体是鳍片,而现在栅极变成了鳍片。所以 GAAFET 和 3D FinFET 在实现原理和思路上有很多相似的地方。

不管怎么说,从三接触面到四接触面,并且还被拆分成好几个四接触面,显然,这次栅极对电流的控制力又进一步提高了。

此外,GAA 的这种设计也可以解决原来鳍片间距缩小的问题,并且在很大程度上解决栅极间距缩小后带来问题,例如电容效应等。

总之,在 GAAFET 技术的巧妙帮助下,半导体制程工艺的进化之路还将进一步往前走,并将成为 5nm 之后大家经常听到的关键词。

2、三星、英特尔和台积电,同样的态度,不同的进展

GAAFET 技术如此重要,显然目前芯片代工的三巨头英特尔、三星和台积电都在积极备战,准备在 5nm 之后的节点上大干一场。

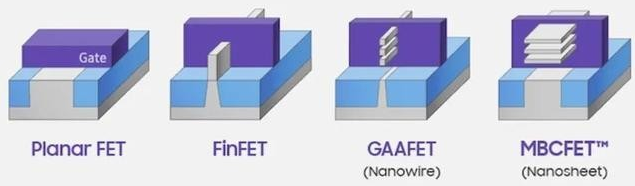

首先要说明的是,前面我们讲到源极到漏极的 “小棍子”,只是举例,实际上也可以是其他形状,例如圆柱状、甚至是板状的等等。

就这一点,目前行业里分几种方案:

纳米线,就是采用圆柱或者方形的截面;板片状,顾名思义,就是源极漏极的半导体设计成水平的板块状,通常会堆叠多个穿透栅极;六角形截面;纳米环技术,就是穿透栅极的半导体为环形截面。在三巨头中,目前最积极高调的是三星,他们采用的是第二种方案,也就是堆叠的板片状方案。目前三星也是三巨头中唯一一家公布自己在 GAA 上详细技术方案的企业。

三星还给自家 GAA 技术取了个独特的名字:Multi-Bridge Channel,简称 MBCFET。

三星表示,他们会在 3nm 这一节点上使用 MBCFET 技术。MBCFET 相比纳米线技术拥有更大的栅极接触面积,从而在性能、功耗控制上会更加出色。

就板片状的技术方案来说,三星透露其目前设计每个晶体管上堆叠 3 条板片,板片厚度为 5nm,板片之间的距离为 10nm,同时栅极长度为 12nm 等。

在具体表现方面,三星还称第一代的 3nm MBCFET 相比 7nm FinFET 会有 35% 的性能提升,功耗会降低 50%,芯片面积则会缩减 45%,电压则可以下降到 0.7V。

三星更是信心满满地表示,2020 年底,他们的 MBCFET 就可以开始风险试产,2021 年有望大规模量产,同时 2021 年他们还会推出第一代 MBCFET 的优化版本。

值得一提的是,三星在 GAA 上也尝试了其他技术方案,不同方案在性能、功率方面的表现也不同,未来可以根据芯片应用场景的差异来匹配对应的方案。

相比三星的激进,台积电这边就相对保守了,目前他们已经表示,3nm 节点上将会继续打磨 FinFET 技术,而不是急于上马 GAAFET。

主要原因是台积电切入 GAA 技术的时间相对晚于三星,同时也为产业链平稳过渡考虑。

至于什么时候会使用 GAA 技术,官方还没有明确公布。但根据外界的消息,台积电会在 2nm 节点上采用 GAA 技术。

台积电已表示,2nm 研发生产将落脚新竹宝山,将规划建设 4 个超大型晶圆厂,投入 8000 名工程师,目前已经交付研发,根据规划,2nm 工艺预计会在 2023 年开始风险试产,2024 年量产。

至于英特尔,按照他们的进度,2021 年会推出 7nm 工艺,采用的仍然是目前的 SuperFinFET,而到 2023 年,他们会在 5nm 这个节点上放弃 FinFET 晶体管,转向 GAA 环绕栅极晶体管。这个消息来自产业链,并非英特尔官方公布,但此前英特尔曾表示,将在 5nm 工艺重新夺回领导地位,由此来看,他们在 2023 年的 5nm 节点上推出 GAA 工艺是大概率会发生的。

3、半导体行业还没有到极限

就像 FinFET 工艺拯救了芯片产业,在 5nm 之后的时代,GAAFET 也将成为带领半导体行业进一步发展的关键。当然,在这背后,每前进一步,都是行业付出巨大努力的结果。

就以 GAA 技术来说,三星透露其自家 3nm GAA 的研发成本比 5nm FinFET 更高,有可能超过 5 亿美元,巨大的研发成本首先就是摆在行业面前的一道坎。

同时 GAAFET 的工艺制造难度也是极高的,具体的细节这里就不说了,最难的地方自然是如何让栅极环绕源极和漏极的纳米线,这里面的工艺极其复杂,也只有对 FinFET 技术炉火纯青的半导体巨头才能应对这样的技术挑战。

此外,和 GAA 技术配套的 EUV 极紫外光刻技术也需要进一步成熟,解决光刻功率不够以及光子噪音等问题。

但好消息时,因为 GAA 相当于传统 FinFET 的 “改良版”,因此生产制造的很多技术细节和步骤是可以共用的,这意味着像三星、台积电和英特尔这些对 FinFET 技术非常熟悉的巨头,在 GAA 技术过渡时可能会比过去更加顺畅,产业化的时间也可能会更短。

最后,IT之家想说的是,GAA 技术的推进,的确在很大程度上推进半导体工艺特别是先进制程上的发展。但随着制程技术越来越接近物理极限,想要把芯片继续做薄做小,先进制程也并不是唯一的道路,材料、封装等也都可以称为突破的道路。

前面我们说到的胡正明教授曾经说过:

FinFE 证实了这个产业还有很多可以用我们的智慧来解决的问题,我还真是看不到半导体产业发的极限。

这句话放在 GAA 上也适用,或者说,只要这个世界仍然对运算有需求,半导体行业的人们就会想出智慧的解决方案来拓宽行业的天花板,用他们的技术让这个世界更加美好。